2010年度 森泰吉郎記念研究振興基金 研究助成金 報告書

IP接続による密結合型分散コンピューティング

慶應義塾大学大学院 政策・メディア研究科 後期博士課程3年

松谷健史

はじめに

コンピュータの処理能力に影響するCPU、メモリ、拡張機器などのハードウェア構成は,物理的な接続によって静的に決定されている。

コンピュータ内部のハードウェアはバスによって接続されているが、バスには距離、デバイスの数、並列トランザクション数、再構成可能性の点で制限がある。

特別に設計されたI/Oネットワークでさえ、それら制限の一部分を解決するにすぎない。

この問題を解決するために、本論文ではIPレベルネットワークをCPUとメモリ、I/Oデバイスのバス相互接続に用いる手法を提案する。

提案内容の一部を実現するために、バスのプロトコルとインターネットプロトコルとを相互に変換するIPバスブリッジを設計し、FPGAボード上に実装、評価した。

IPバスブリッジはRISCアーキテクチャ CPUとメモリと拡張機器をEthernetによって接続しており、IPを使用した接続と使用しない接続の両方に対応している。

なお、本年度は前年度に対しておもに下記の設計と実装をおこなった

•

本アーキテクチャ向けLinux KernelのSMP対応

arch/lm32/include/asm/*

arch/lm32/kernel/

•

IP接続によるSMP接続回路機構の設計と実装

Inter-Processor Interrupt回路の新規設計と実装

ローカルタイマー割り込み回路の新規設計と実装

• 本研究によるLinux KernelソースのWeb公開

2010年度助成 金は、FPGAによる回路を論理合成するためのソフトウェアライセンスと論理合成・シミュレーション用 PCに当てた。

研究成果

・成果物1:本アーキテクチャをFPGA回路上にて実装したコンピュータのSMP化

・成果物2:成果物1上で動作するLinux 2.6.38-rc8 最新 Kernelの移植とBusyboxによる実行環境の構築

・Web公開:本アーキテクチャ用に移植したソフトIP CPU(Lattice Mico32)向けLinux Kernel

本研究の目的

本研究の目的はインターネット上においてアプリケーションやユーザの要求に応じてハードウェアを動的に割り当てるコンピュータアーキテクチャを実現するために、バスの距離と数の制限に関する問題を解決することである。

そのためにハードウェアの拡張をおこなう際に重要となる、バスの距離と数の制限を解決する必要がある。

1.距離の制限

距離の制限とは、CPUやメモリ、周辺装置を増設するバスは主に匡体の中にあるため、接続できる距離に限界があることを示す。

2.数の制限

数の制限とは、物理的なバスの接続数や仕様によってハードウェア増設できる数が制限されてしまうことを示す。

3.アクセス遅延の制限

アクセス遅延の制限とは、メモリやI/Oに対して遅いバスなどを用いることによりアクセスに一定時間以上の遅延がかかりタイムアウトや性能の著しい低下などを招き利用を制限されることを示す。

本研究ではネットワーク技術を使い、IPとハードウェアのバスレベルのプロトコル変換ができる専用のバスブリッジを設計することにより、バスの距離と数の制限に関する問題、メモリーのレプリケーション機構によってアクセス遅延の制限を解決する。

解決へのアプローチ

上記の問題を解決するために、次のようなアプローチをとる。

1. グローバル接続

コンピュータバスには距離や接続数の制限がある。本機構ではバス信号を既存の通信ネットワークプロトコルに変換する機能をもつことによりグローバル接続を実現する。

2. 透過的アクセス

接続先の回路がローカル上にある場合でも、ネットワークを超えたリモート上にある場合でも意識することなく透過的に利用できる必要がある。また、回路が直接通信ネットワークプロトコルで接続することは回路規模の増加や互換性の低下につながるため、回路間にブリッジ機構を設けることにより実現する。

3. 低遅延

リモート回路への接続ではネットワークプロトコルへ変換されるため遅延の増加がみこまれる。本機構では低遅延化を実現するために、ネットワークプロトコルへの変換にソフトウェア処理は一切おこなわず、電子回路のデータフロー処理によってネットワーク処理を実現できる専用のLANコントローラを設計する。

4. リモート接続におけるメモリ遅延対策

メモリ回路がリモートにある場合において、ワード単位でネットワークを経由して頻繁にアクセスを行うと遅延の影響は大きく、使用用途によっては現実的ではない。

本機構では、ブリッジ内にメモリーレプリケーション機構を設計することでリモートメモリとのアクセス回数を大幅に削減し遅延の問題を軽減化させる。

5. 柔軟性のある回路接続

通常、バスに接続される回路は同一バス内のCPUやメモリとしか接続が行われることがなく、ハードウェアの構成変更がない限り接続先は固定となる。本設計ではネットワークを経由して様々な回路と動的に接続するための機構が必要になる。

IPバスコンピュータの設計

実装の対象は本機構を持つブリッジ回路とCPU、Video回路、Ethernet回路、PS2インターフェイス回路、UART回路とする。

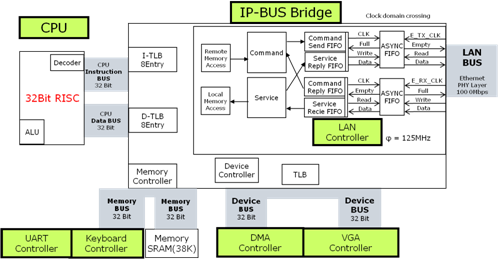

全体図の概要を図 1に示す。

図1: 設計概要

IPバスコンピュータの実装

本研究で設計したIPバスココンピュータの有用性を調べていくために市販のFPGAボード上に回路を構築した。

FPGAボードおよび開発環境を下記に示す。

FPGAボード

|

FPGAボード |

Xilinx ML401/402ボード |

|

MEMORY回路 |

DDR-SDRAM 64MB |

|

Ethernet回路 |

10/100/1000M Ethernet (PHY) |

|

VGA回路

|

16bit DAC (クロック75MHz) |

|

SMP回路 |

IPI, Local Timer |

|

ブリッジ回路 |

IP/BUS Wired 変換 |

開発環境

|

使用言語 |

Verilog HDL言語 |

|

論理合成ツール |

Xilinx ISE 12.3 Foundation |

|

回路シミュレータ |

Xilinx Simulator および Veritak Win |

写真1: FPGAボード上に回路を実装したIPバスコンピュータ

本年度のまとめ

昨年度までの成果に対し、Linux のSMP Kernelに対応させるためSMP化に必要な電子回路の設計・実装およびSMP Kernelの開発を行ない、同一ボード上での動作確認をすることが出来た。

今後の課題として複数ボード間でのSMP接続の品質・性能向上、より多くのAPIの対応、ライブラリー、アプリケーションの充実など、一般利用を考慮した研究・開発を進める。

出展・発表 (2010年度)

WIDE研究会,2010/9, 2011/3

ORF2010,六本木ヒルズ

写真2:Ethernetで接続した2つのCPUによるMulti Processorの実演デモ (ORF2010)